要说这两年芯片行业最热闹的话题,那绝对绕不开“双芯片”或者叫“多芯片”这个设计思路。这可不是简单地把两个芯片粘在一起,而是一种从底层改变我们造芯片、用芯片的哲学。以前大家拼命追求的是“一颗更强大的单芯片”,现在行业更倾向于思考“如何让多颗芯片高效协同工作”。这种转变背后,既有现实的无奈,也充满了智慧的光彩-7。

咱们都听说过“摩尔定律”这词儿,它就像芯片行业的紧箍咒,又像是指路明灯。简单说,就是芯片上的晶体管每隔一段时间就能缩小一点、变多一倍,性能也跟着翻番。但这活儿现在越来越难干了,晶体管小到快接近物理极限,设计制造一颗庞大又完美的单芯片,成本高得吓人,良品率还不一定好看-3。这就好比以前盖房子,总想在一块地上盖出摩天大楼,但地基和建材快到极限了,楼越高越不稳当。这时候,聪明的工程师们就想,咱为啥不换个思路,用几栋高度专业化的楼,通过高效的走廊(就是先进封装和互连技术)连成一个功能强大的建筑群呢?这就是双芯片技术乃至更广泛的Chiplet(小芯片)技术最核心的出发点-7。

这种“建筑群”式的芯片,玩法可多了,绝不是千篇一律。从台积电这样的制造巨头,到苹果这样的产品王者,再到IBM这样的基础研究先锋,都在用自己的方式实践。

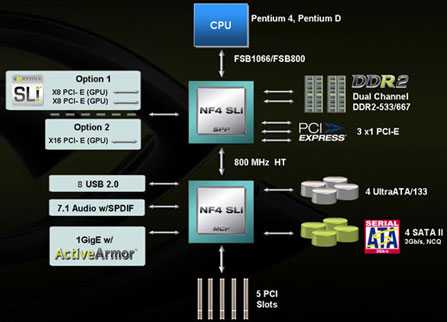

一种很主流的玩法是“肩并肩”的2.5D封装。比如早在2019年,台积电就在研讨会上展示过一款自研芯片,它采用了7纳米工艺,但里面并不是单一的一块硅片,而是由两个小芯片(Die)并排封装在一起。其中一个芯片专注于高性能计算,内置了4个Arm Cortex-A72核心;另一个芯片则是个“大仓库”,专门装了6MB的三级缓存-2。它们通过芯片下层的硅中介层或先进封装基板高速互联,既能各自发挥特长,又能紧密合作,这就比把所有功能都挤在一块大硅片上要灵活、经济得多。

更激进的还有“上下楼”的3D堆叠。这就像盖楼房,把不同功能的芯片层垂直叠起来,它们之间的通信距离缩短到微米级,速度快得惊人,还能极大节省面积。有传闻说,苹果正在为2026年的iPhone(比如可能叫iPhone 18 Pro)规划全新的A20系列芯片,可能就会首次采用一种叫做“晶圆级多芯片模块”(WMCM)的封装技术-4。这种技术据说能让处理器(SoC)和内存(DRAM)等不同元件在晶圆阶段就整合好,无需额外的连接基板,目标是大幅改善数据交换的效率和散热的性能-4。如果成真,这将是手机芯片设计的一次重大飞跃。

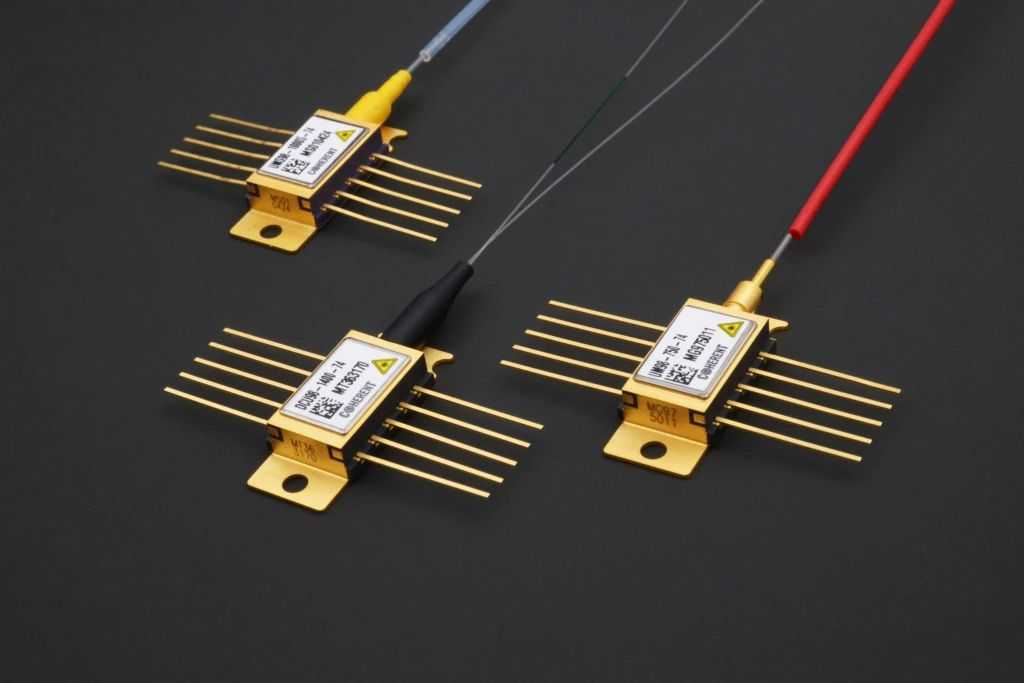

而在一些前沿领域,双芯片技术的形态更加颠覆想象力。比如,康奈尔大学的研究人员就和波兰科学院合作,捣鼓出了一种“双面芯片”-5。他们利用氮化镓(GaN)这种半导体材料的特殊极性,在一面制造高电子迁移率晶体管(一种高性能开关),在另一面制造发光二极管(LED)-5。等于把光和电的主动部件集成在了同一块芯片的正反两面,这在以前是从未有过的。这种创新为未来更紧凑、功能融合的微显示和光通信芯片打开了新世界的大门-5。

还有更“未来”的。IBM在量子计算领域推出的Nighthawk和Loon芯片,虽然具体细节不同,但也体现了利用特定功能模块(可以理解为一种特殊的“芯片”)组合来构建复杂计算系统的思路,目标是在2026年前实现特定任务的“量子优势”-1。

这股“双芯片”风潮到底解决了咱们啥实际问题?这可不是工程师们的自娱自乐。

它直面了“成本”这个最现实的痛点。清华大学的一位博士甚至提出了“Chiplet精算师”的成本模型-3。道理很简单:制造一片大型硅片,只要有一个微小缺陷,整片都可能报废,成本血本无归。而把大系统拆成几个更小、工艺可能不同的芯片来制造,单个的良品率更高,总体成本反而可能下降-3。特别是对于最顶尖的制程(比如3nm、2nm),这种成本优势越发明显-3。这就好比印刷海报,印一张全开的大海报,错一个点整张废了;不如分成几张A4纸分别印,再拼起来,成功率更高。

它给了产品设计前所未有的“灵活性”和“迭代速度”。Arm在2026年的技术预测里就特别强调,模块化的小芯片设计让厂商可以像搭积木一样,混合搭配不同工艺、不同供应商的计算核心、专用加速器(比如AI引擎)、内存模块等-7。想升级AI性能?换一个新的AI小芯片模块就行,不用重新设计整个庞大的系统。这极大地降低了创新门槛,缩短了产品开发周期-7。

再者,它对“性能瓶颈”的突破是实实在在的。像前面提到的苹果可能采用的WMCM技术,目的之一就是让处理器和内存“贴得更近”,数据传输的路径更短、带宽更大、延迟更低,这对于手机运行大型游戏和AI应用至关重要-4。在服务器和数据中心领域,通过先进封装将计算芯片和高带宽内存(HBM)3D堆叠在一起,已经成为提升AI算力标配手段。

当然,任何技术都不是银弹,双芯片设计也有自己的“坎儿”。最头疼的就是“散热”和“互连损耗”。把那么多高性能模块封装在方寸之间,热量如何快速导出是个大学问。历史上,英特尔和AMD早期的一些多芯片封装产品,就曾因为功耗和散热问题影响了最终性能表现-9。芯片之间高速通信的能耗和信号完整性,也是极大的工程挑战。这就像建筑群,楼盖得再漂亮,如果走廊狭窄拥堵、通风不畅,整个系统的效率也会大打折扣。

展望未来,双芯片乃至多芯片集成这条路,只会越走越宽。它不仅是一种封装技术,更是一种系统设计理念的革新。随着台积电、三星等厂商在2nm、1.4nm等更先进制程上的推进,以及CoWoS、SoIC等封装技术的不断成熟,我们有理由相信,未来的芯片将是“混搭”的艺术:核心计算部分用最顶级的3nm/2nm工艺,I/O接口、模拟电路等可以用更成熟经济的12nm/28nm工艺,通过先进封装浑然一体-10。

总而言之,双芯片技术从本质上讲,是半导体行业在物理极限和经济效益双重压力下,一次精彩的“突围”和“进化”。它不再执念于雕刻一枚完美的“单晶圣杯”,而是致力于构建一个高效协同的“芯片城邦”。对于咱们普通用户来说,这意味着未来的手机、电脑、汽车乃至各种智能设备,能在功耗不变甚至更低的情况下,获得更强大、更专门化的计算能力。下一次当你感叹手机AI修图又快又准,或者电脑同时处理多任务依然流畅时,或许背后就有着这些“双芯”乃至“多芯”协作的默默功劳。芯片的世界,正从孤独求败的“单核王者”,走向众志成城的“团队英雄”时代。